美光:下一代DRAM技术面临哪些困境?

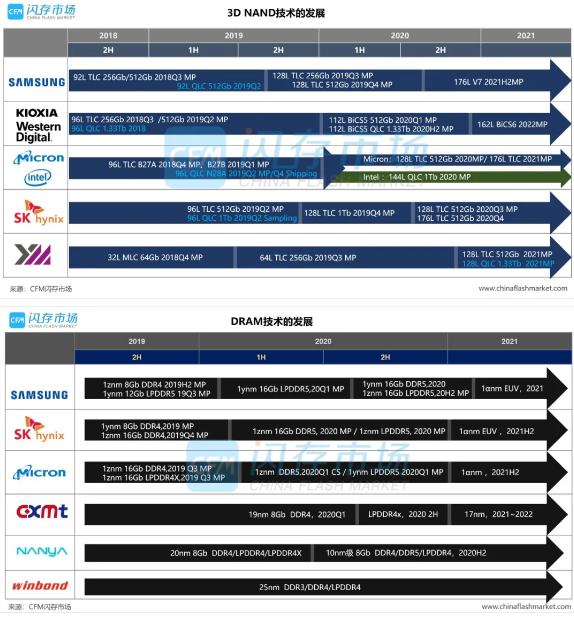

近年来,在原厂之间的技术角逐之中,美光可谓成绩亮眼,无论在DRAM还是NAND领域都可谓“一马当先”,不仅率先批量生产176层3D NAND Flash,也是第一个宣布批量出货1α DRAM产品的厂商。

另外,在DRAM领域,美光更是三家内存原厂中唯一在1α制程中没有导入EUV工艺的厂商。近日有报道称,美光最新1α制程产品拥有0.315Gb/mm²的存储密度,half pitch为14.3nm,超越了三星1z制程工艺0.299 Gb/mm²的存储密度,是当前业内存储密度最高的产品。

那么,美光作为DRAM技术发展的有力推手,在下一代DRAM技术中面临哪些技术和性能挑战?无疑对产业链具有借鉴作用。在一次技术交流会上,美光对此做了详细阐述,并以《Scaling and Performance Challenges of Future DRAM》为题公开发表。

Row Hammer攻击

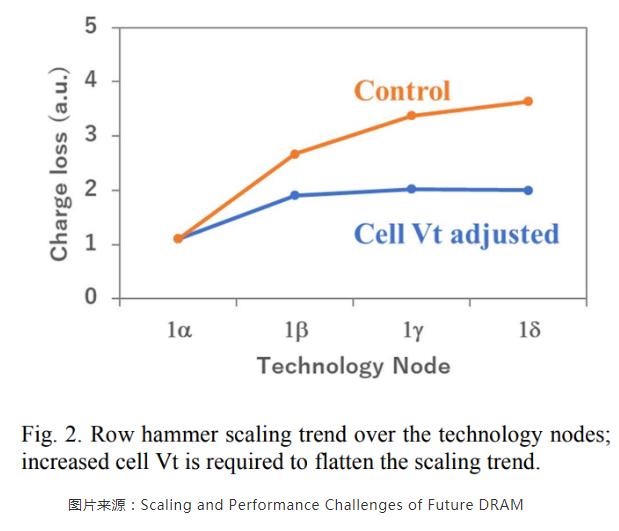

所谓Row Hammer攻击是指为了内存容量的增加,DRAM cell越做越小且距离越来越近,导致存储器单元泄露电荷并可能造成比特翻转的意外情况。

Row Hammer问题并非新增问题,并将在DRAM微缩过程中愈发严重。虽然,当前通过采用ECC纠错技术缓解了这种情况,却仍然存在一定的限制。而在1β制程技术中,若要缓解Row Hammer问题,则需要突破性技术改善。

刷新周期

所谓刷新周期是指对所有DRAM存储单元恢复一次原状态所需的时间间隔。由于DRAM的存储位元是基于电容器的电荷存储,这个电荷量会随着时间和温度而减少,因此必须定期的刷新,以保持它们原来记忆的正确信息。

根据公式,刷新周期与单位电容成正比,随着DRAM技术尺寸微缩,刷新周期性能也将下降。另外,在一定刷新周期内,错误率也将随着温度的升高而增加。而这一特性限制了产品在汽车领域的使用,因为在汽车领域中,通常对器件的温宽要求很高。

随着DRAM器件尺寸微缩,感测容限不断降低,且由于每个节点的窄通道效应和短通道效应,感测放大器晶体管Vt的变化加剧。

CMOS技术

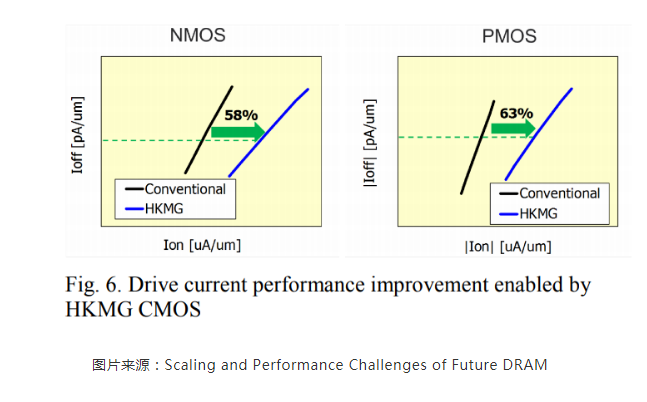

随着CMOS电路不断缩小,晶体管的关键指标:栅氧厚度不断缩小,然而当厚度缩小到2nm以下时,就会出现明显的隧穿泄露。因此逻辑芯片厂商开始使用High-K工艺,就是使用高介电常数的物质替代二氧化硅。

近十年中,DRAM芯片中也使用了High-K工艺,使得DRAM性能提升的同时降低功耗。在DRAM历史上,随着数据速率提高以及功耗要求提升,DRAM工作电压已经从5V降低到1.05V。随着DRAM性能要求的分化,CMOS性能有望缩小与逻辑CMOS之间的差距。

随着数据量增加以及对器件性能要求的提升,在实现1α以下DRAM技术的发展过程中将面临许多挑战。存储厂商将不断开创创新的工艺与材料开发来克服这些挑战,持续提供突破和创新的设计方法,满足未来的性能及规模需求。