三星芯片,亏损1.2万亿

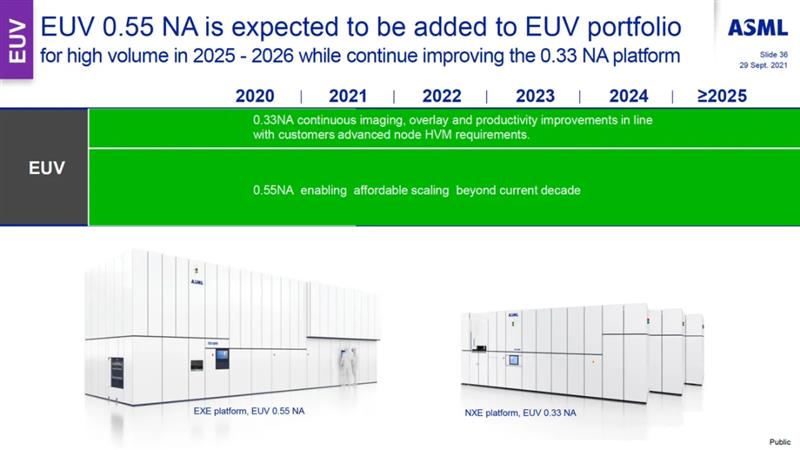

本周,英特尔(Intel)开始接收其台 ASML 的数值孔径为 0.55(High-NA)的极紫外光(EUV)光刻工具,英特尔将利用这台工具学习如何使用该技术,然后在未来几年左右将机器部署到 18A 后生产节点。华兴资本(China Renaissance)和SemiAnalysis的分析师都认为,相比之下,台积电并不急于在短期内采用高NA EUV,该公司可能要在2030年或更久以后才会加入这一行列。

图源:ASML

"华兴资本(China Renaissance)和 SemiAnalysis 的分析师 Szeho Ng 写道:"与英特尔在转向 GAA(计划于 [20A] 推出)后不久就使用高纳超高真空(High-NA EUV)相比,我们预计台积电将在 N1.4 后时代(拐点可能在 N1,计划于 2030 年后推出)推出高纳超高真空(High-NA EUV)。

英特尔积极的工艺技术路线图包括:从20A(20埃,2纳米级)开始采用RibbonFET全栅极(GAA)晶体管和PowerVia背面功率传输网络(BSPDN),然后在18A的基础上进行改进,然后在18A之后的节点上开始使用High-NA EUV工具,以提供功率、性能和面积特性以及的周期时间。

配备 0.33 数值孔径透镜(Low-NA)的现代 EUV 光刻工具可为量产提供 13 至 16 nm 的临界尺寸,这足以生产出 26 nm 的金属间距,以及估计为 25 至 30 nm 的端到端互连空间间距(使用单次曝光图案化)。这对于 3nm 级工艺技术(金属间距在 21 到 24nm 之间)来说已经足够,但在 2nm 及更高的工艺技术中,金属间距将缩小到大约 18 到 21nm(根据 imec 的说法),这就需要使用 EUV 双图案化、图案成型设备或 High-NA 单图案化。

英特尔计划从 20A(即将进入 HVM)开始加入图案整形,然后从 18A 后节点开始加入 High-NA EUV,从而降低工艺流程的复杂性,避免使用 EUV 双图案。然而,High-NA EUV 光刻工具要比 Low-NA EUV 扫描仪贵得多,但 High-NA EUV 有许多特殊性,包括曝光场减少 2 倍。

因此,SemiAnalysis 和华兴资本的分析师认为,使用 High-NA EUV 机器的成本可能高于使用 Low-NA EUV 双图案化技术,至少在初期是这样,这就是为什么台积电可能暂时不倾向于使用这种技术,以确保低成本,尽管代价是生产复杂性和可能较低的晶体管密度。

"Szeho Ng解释说:"低NA EUV多重图案化,尽管在更多曝光通道上的吞吐量较低,但在初的GAA尝试中,成本仍可能低于高NA EUV;高NA EUV的源功率更高,可驱动更精细的CD(临界尺寸),加快了投影光学器件和光掩模的磨损,超过了更高吞吐量的优势。"这与台积电以成本竞争力的技术瞄准批量市场的做法不谋而合"。

台积电于 2019 年开始将极紫外光(EUV)光刻工具用于芯片的大批量生产,这比三星代工晚了几个月,但比英特尔早了好几年。英特尔希望在High-NA EUV方面领先于三星代工和台积电,这可以确保一些战术和战略利益。的问题是,如果台积电到 2030 年或更晚(即比英特尔晚 4 到 5 年)才采用 High-NA 光刻技术,它还能保持工艺技术的领先地位吗?